Using Heavy Copper and EXTREME Copper in PCB Design and Fabrication for Maximum Reliability By Epec Engineered Technologies

An increasing number of power electronics products are taking advantage of a growing trend in the printed circuit board industry: Heavy Copper Printed Circuit Boards.

Most commercially available PCBs are manufactured for low-voltage/low power applications, with copper traces/planes made up of copper weights ranging from 1/2 oz/ft2 to 3 oz/ft2. A heavy copper circuit is manufactured with copper weights anywhere between 4 oz/ft2 to 20 oz/ft2. Copper weights above 20 oz/ft2 and up to 200 oz/ft2 are also possible and are referred to as EXTREME Copper. Our discussion will focus primarily on Heavy Copper.

The construction of a heavy copper circuit endows a board with benefits such as:

- Increased endurance to thermal strains.

- Increased current carrying capacity.

- Increased mechanical strength at connector sites and in PTH holes.

- Use of exotic materials to their full potential (i.e., high temperature) without circuit failure.

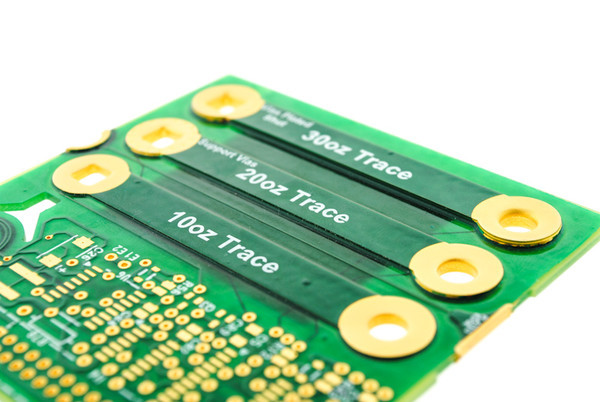

- Reduced product size by incorporating multiple copper weights on the same layer of circuitry (see Figure 1).

- Heavy copper plated vias carry higher current through the board and help to transfer heat to an external heatsink.

- On-board heatsinks directly plated onto the board surface using up to 120-oz copper planes.

- On-board high-power-density planar transformers

Figure 1. Sample featuring 2oz, 10oz, 20oz, and 30oz copper features on the same layer.

Figure 1. Sample featuring 2oz, 10oz, 20oz, and 30oz copper features on the same layer.

Heavy Copper Circuit Construction

Standard printed circuit boards, whether double-sided or multilayer, are manufactured using a combination of copper etching and plating processes. Circuit layers start as thin sheets of copper foil (generally 0.5 oz/ft2 to 2 oz/ft2) that are etched to remove unwanted copper, and plated to add copper thickness to planes, traces, pads and plated-through-holes. All of the circuit layers are laminated into a complete package using an epoxy-based substrate, such as FR4 or polyimide.

Boards incorporating heavy copper circuits are produced in exactly the same way, albeit with specialized etching and plating techniques, such as high-speed/step plating and differential etching. Historically, heavy copper features were formed entirely by etching thick copper clad laminated board material, causing uneven trace sidewalls and unacceptable undercutting. Advances in plating technology have allowed heavy copper features to be formed with a combination of plating and etching, resulting in straight sidewalls and negligible undercut.

Plating of a heavy copper circuit enables the board fabricator to increase the amount of copper thickness in plated holes and via sidewalls. It's now possible to mix heavy copper with standard features on a single board, also known as PowerLink. Advantages include reduced layer count, low impedance power distribution, smaller footprints and potential cost savings. Normally, high-current/high-power circuits and their control circuits were produced separately on separate boards. Heavy copper plating makes it possible to integrate high-current circuits and control circuits to realize a highly dense yet simple board structure. Browse through our blog for more information, Heavy and Extreme Copper PCBs: Hole Sized, Trace Widths, and Spacing.

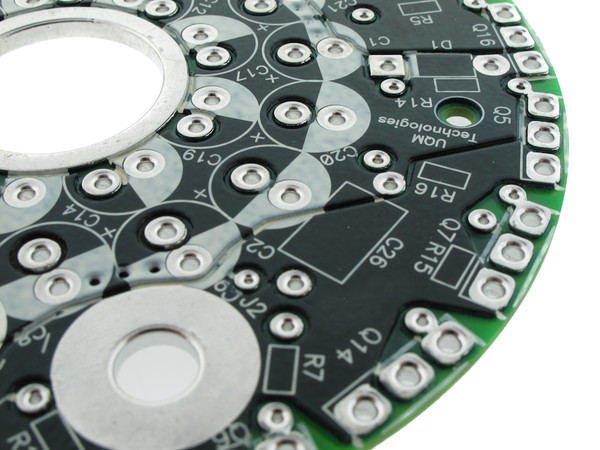

The heavy copper features can be seamlessly connected to standard circuits. Heavy copper and standard features can be placed with minimal restriction provided the designer and fabricator discuss manufacturing tolerances and abilities prior to final design (Figure 2).

Figure 2. 2oz features connect control circuits while 20oz features carry high current loads.

Figure 2. 2oz features connect control circuits while 20oz features carry high current loads.

Current Carrying Capacity and Temperature Rise

The amount of current a copper circuit can safely carry depends on how much heat rise a project can withstand, since heat rise and current flow are related. When current flows along a trace, there is an I2R (power loss) that results in localized heating. The trace cools by conduction (into neighboring materials) and convection (into the environment). Therefore, to find the maximum current a trace can safely carry, we must find a way to estimate the heat rise associated with the applied current. An ideal situation would be to reach a stable operating temperature where the rate of heating equals the rate of cooling. An IPC formula can be used to model this event.

| Track Width (inch) | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Cu weight (oz/ft2) | Thickness (inch) | 0.0625 | 0.1250 | 0.2500 | 0.5000 | 1.0000 | 2.0000 | 4.0000 | 8.0000 | 16.0000 |

| 1 | 0.0014 | 4.6 | 7.6 | 12.5 | 20.7 | 34.2 | 56.6 | 93.6 | 154.7 | 255.6 |

| 2 | 0.0028 | 7.6 | 12.5 | 20.7 | 34.2 | 56.6 | 93.6 | 154.7 | 255.6 | 422.5 |

| 4 | 0.0056 | 12.5 | 20.7 | 34.2 | 56.6 | 93.6 | 154.7 | 255.6 | 422.5 | 698.4 |

| 6 | 0.0084 | 16.8 | 27.8 | 46.0 | 76.0 | 125.5 | 207.5 | 343.0 | 566.9 | 937.1 |

| 8 | 0.0112 | 20.7 | 34.2 | 56.6 | 93.6 | 154.7 | 255.6 | 422.5 | 698.4 | 1154.4 |

| 10 | 0.0140 | 24.4 | 40.3 | 66.5 | 110.0 | 181.8 | 300.5 | 496.7 | 821.1 | 1357.1 |

| 12 | 0.0168 | 27.8 | 46.0 | 76.0 | 125.5 | 207.5 | 343.0 | 566.9 | 937.1 | 1548.9 |

| 14 | 0.0196 | 31.1 | 51.4 | 84.9 | 140.4 | 232.0 | 383.6 | 634.0 | 1047.9 | 1732.1 |

| 16 | 0.0224 | 34.2 | 56.6 | 93.6 | 154.7 | 255.6 | 422.5 | 698.4 | 1154.4 | 1908.1 |

| 18 | 0.0252 | 37.3 | 61.7 | 101.9 | 168.4 | 278.4 | 460.2 | 760.7 | 1257.3 | 2078.2 |

| 20 | 0.0280 | 40.3 | 66.5 | 110.0 | 181.8 | 300.5 | 496.7 | 821.1 | 1357.1 | 2243.2 |

| 24 | 0.0336 | 46.0 | 76.0 | 125.5 | 207.5 | 343.0 | 343.0 | 937.1 | 1548.9 | 2560.2 |

| 28 | 0.0392 | 51.4 | 84.9 | 140.4 | 232.0 | 383.6 | 634.0 | 1047.9 | 1732.1 | 2863.0 |

| 32 | 0.0448 | 56.6 | 93.6 | 154.7 | 255.6 | 422.5 | 698.4 | 1154.4 | 1908.1 | 3154.0 |

| 36 | 0.0504 | 61.7 | 101.9 | 168.4 | 278.4 | 460.2 | 760.7 | 1257.3 | 2078.2 | 3435.1 |

| 40 | 0.0560 | 66.5 | 110.0 | 181.8 | 300.5 | 496.7 | 821.1 | 1357.1 | 2243.2 | 3707.8 |

| 45 | 0.0630 | 72.5 | 119.8 | 198.0 | 327.3 | 541.0 | 894.3 | 1478.1 | 2443.2 | 4038.3 |

| 50 | 0.0700 | 78.2 | 129.3 | 213.7 | 353.3 | 584.0 | 965.2 | 1595.5 | 2637.1 | 4358.9 |

| 55 | 0.0770 | 83.8 | 138.6 | 229.0 | 378.6 | 625.7 | 1034.3 | 1709.6 | 2825.8 | 4670.8 |

| 60 | 0.0840 | 147.6 | 244.0 | 403.2 | 666.5 | 1101.7 | 1820.9 | 3009.8 | 4974.9 | |

| 70 | 0.0980 | 165.0 | 272.8 | 450.9 | 745.3 | 1231.9 | 2036.2 | 3365.7 | 5563.1 | |

| 80 | 0.1120 | 181.8 | 300.5 | 496.7 | 821.1 | 1357.1 | 2243.2 | 3707.8 | 6128.6 | |

| 90 | 0.1260 | 198.0 | 327.3 | 541.0 | 894.3 | 1478.1 | 2443.2 | 4038.3 | 6675.0 | |

| 100 | 0.1400 | 213.7 | 353.3 | 584.0 | 965.2 | 1595.5 | 2637.1 | 4358.9 | 7204.8 | |

| 120 | 0.1680 | 403.2 | 666.5 | 1101.7 | 1820.9 | 3009.8 | 4974.9 | 8223.0 | ||

| 140 | 0.1960 | 450.9 | 745.3 | 1231.9 | 2036.2 | 3365.7 | 5563.1 | 9195.3 | ||

| 160 | 0.2240 | 496.7 | 821.1 | 1357.1 | 2243.2 | 3707.8 | 6128.6 | 10130.0 | ||

| 180 | 0.2520 | 541.0 | 894.3 | 1478.1 | 2443.2 | 4038.3 | 6675.0 | 11033.1 | ||

| 200 | 0.2800 | 584.0 | 965.2 | 1595.5 | 2637.1 | 4358.9 | 7204.8 | 11908.9 | ||

IPC-2221A, calculation for current capacity of an external track [1]:I = .048 * DT(.44) * (W * Th)(.725)

Where I is current (amps), DT is temperature rise (°C), W is width of the trace (mil) and Th is thickness of the trace (mil). Internal traces should be derated by 50% (estimate) for the same degree of heating. Using the IPC formula, we generated Figure 3 (see table at end of text), showing the current carrying capacity of several traces of differing cross-sectional areas with a 20°C temperature rise.

What constitutes an acceptable amount of heat rise will differ from project to project. Most circuit board dielectric materials can withstand temperatures of 100°C above ambient, although this amount of temperature change would be unacceptable in most situations.

Circuit Board Strength and Survivability

Circuit board manufacturers and designers can choose from a variety of dielectric materials, from standard FR4 (operating temp. 130°C) to high-temperature polyimide (operating temp. 250°C). A high-temperature or extreme environment situation may call for an exotic material, but if the circuit traces and plated vias are standard 1 oz/ft2, will they survive the extreme conditions? The circuit board industry has developed a test method for determining the thermal integrity of a finished circuit product. Thermal strains come from various board fabrication, assembly and repair processes, where the differences between the coefficient of thermal expansion (CTE) of Cu and the PWB laminate provide the driving force for crack nucleation and growth to failure of the circuit. Thermal cycle testing (TCT) checks for an increase in resistance of a circuit as it undergoes air-to-air thermal cycling from 25°C to 260°C.

An increase in resistance indicates a breakdown in electrical integrity via cracks in the copper circuit. A standard coupon design for this test utilizes a chain of 32 plated through holes, which has long been considered to be the weakest point in a circuit when subjected to thermal stress.

The TCT results clearly show that the failure rate, no matter what the board material, can become unacceptable. Thermal cycle studies done on standard FR4 boards with 0.8-mil to 1.2-mil copper plating have shown that 32% of circuits fail after eight cycles (a 20% increase in resistance is considered a failure). Boards with exotic materials show significant improvements to this failure rate (3% after eight cycles for Cyanate Ester), but are prohibitively expensive (five to 10 times material cost) and difficult to process. An average surface-mount technology assembly sees a minimum of four thermal cycles before shipment, and could see an additional two thermal cycles for each component repair.

Using heavy copper circuits would reduce or eliminate these failures altogether. Plating of 2 oz/ft2 of copper to a hole wall reduces the failure rate to almost zero (TCT results show a 0.57% failure rate after eight cycles for standard FR4 with a minimum of 2.5-mil copper plating). In effect, the copper circuit becomes impervious to the mechanical stresses placed on it by the thermal cycling.

Thermal Management

As designers strive to obtain maximum value and performance from their projects, printed circuits are becoming more complex and are driven to higher power densities. Miniaturization, use of power components, extreme environmental conditions and high-current requirements increase the importance of thermal management. The higher losses in the form of heat, that's often generated in the operation of electronics, has to be dissipated from its source and radiated to the environment; otherwise, the components could overheat and failures may result. However, heavy copper circuits can help by reducing the I2R losses and by conducting heat away from valuable components, reducing failure rates dramatically.

In order to achieve proper heat dissipation from heat sources in and on the surface of a circuit board, heatsinks are employed. The purpose of any heatsink is to dissipate heat away from the source of generation by conduction and emit this heat by convection to the environment. The heat source on one side of the board (or internal heat sources) is connected by copper vias (sometimes called "heat vias") to a large bare copper area on the other side of the board.

Generally, classical heatsinks are bonded to this bare copper surface by means of a thermally conductive adhesive or in some cases, are riveted or bolted. Most heatsinks are made of either copper or aluminum.

The assembly process required for classical heatsinks consists of three labor-intensive and costly steps. The time and work required to complete this process is significant, and the results are inferior to a mechanically automated process. In contrast, built-in heatsinks are created during the printed circuit board manufacturing process and require no additional assembly. Heavy copper circuit technology makes this possible. This technology allows the addition of thick copper heatsinks virtually anywhere on the outer surfaces of a board. The heatsinks are electroplated on the surface and thus connected to the heat conducting vias without any interfaces that impede thermal conductivity.

Another benefit is the added copper plating in the heat vias, which reduces the thermal resistance of the board design, realizing that they can expect the same degree of accuracy and repeatability inherent in PCB manufacturing. Because planar windings are actually flat conductive traces formed on copper clad laminate, they improve the overall current density compared to cylindrical wire conductors. This benefit is due to minimization of skin effect and higher current-carrying efficiency.

On-board planars achieve excellent primary-to-secondary and secondary-to-secondary dielectric isolation because the same dielectric material is used between all layers, ensuring complete encapsulation of all windings. In addition, primary windings can be spilt so that the secondary windings are sandwiched between the primaries, achieving low leakage inductance. Standard PCB lamination techniques, using a choice of a variety of epoxy resins, can safely sandwich up to 50 layers of copper windings as thick as 10 oz/ft2.

During the manufacture of heavy copper circuits, we are usually dealing with significant plating thicknesses; therefore, allowances must be made in defining trace separations and pad sizes. For this reason, designers are advised to have the board fabricator on board early in the design process. Epec Engineered Technologies has developed a set of design guidelines for heavy copper circuits that give designers a basic overview of what is required.

Military Applications

Traditionally when PCBs are used in military applications the designer creates the high current circuits by adding duplicate layers of 3 or 4 oz copper in parallel and crossing their fingers that the layers share the current evenly between them. In practice, the sharing is less than ideal so some layers tend to carry a higher percentage of the load and generate higher losses. Overall, the board normally runs hotter than estimated during the design.

Utilizing Heavy or EXTREME Copper in creating the high current circuits combined with thicker copper plating in the vias and plated through holes will eliminate the need to add duplicate layers in parallel, thereby eliminating any concern of load sharing among multiple layers. Temperature rise due to losses in the boards can be calculated with greater certainty. The thick copper plating in the holes dramatically reduces failures associated with thermal stress. The result is a cooler running and more reliable PCB.

Heavy Copper, EXTREME Copper or PowerLink have been used in the following military applications:

- Weapons Control Systems

- Power Supplies for Radar Systems

- Primary and Secondary Windings of High Power Planar Transformers

- Power Distribution Panels

- Battery Charger and Monitoring Systems

Power electronics products using heavy copper circuitry have been in use for many years in the military and aerospace industry and are gaining momentum as a technology of choice in industrial applications. It's believed that market requirements will extend the application of this type of product in the near future.

References:

[1] IPC -2221A

Looking For a Heavy Copper or EXTREME Copper PCB Design?

Our team of engineers can help you design the most cost-effective heavy copper circuit board, manufactured to the highest quality standards.

Request a Quote Request Design Support